ISD 為一專利申請中的 de-embedding 工具,其可用來取代 TRL 的校正並節省在 SMA 以及板材上的花費,而同時又提供 causal 以及更加精確的 DUT 結果

若您曾經需要進行 TRL 的校正,將會發現 AtaiTec 的 in situ de-embedding (ISD)技術尤其有幫助。相較於 TRL 校正板上超過7個的 test coupons, ISD 僅需要1個。 TRL 需要校正板及 DUT 的 test fixture 具有相同的特性阻抗,但事實上無法達成,此外,TRL 無法去除 lead-in traces 間的耦合效應,以至於 DUT 的 S 參數在 TRL 校正後幾乎總是 non-causal 而難以與模擬結果相關聯(correlate)。 ISD 則可透過簡單的步驟來應對前述問題: (a) 量測 through trace 的 test coupon (只需相似並不需要完全相同,做為 DUT 的 test fixture), (b) 量測 DUT + test fixture, (c) 執行 ISD 軟體。

在 4-port 的 VNA 量測下,從 DUT + test fixture 上去除 SMA 以及lead-in traces 效應後之結果如下圖。

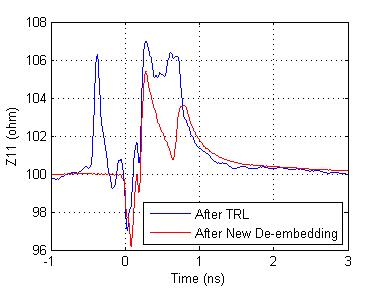

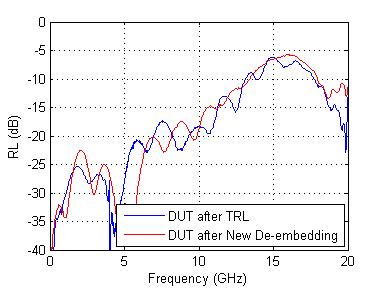

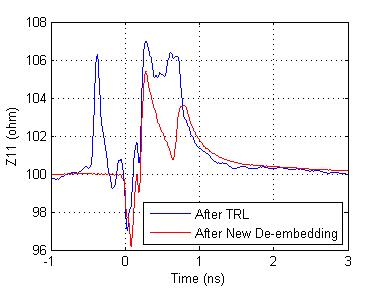

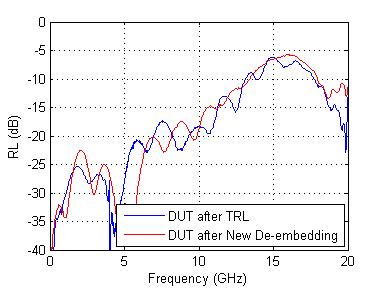

由於 TRL 校正板以及實際 DUT test fixture 之間仍存在阻抗的差異,導致如下圖的 non-causal 現象。 而 ISD 的結果可校正此現象,也可同時觀察 return loss 的結果也大不相同。

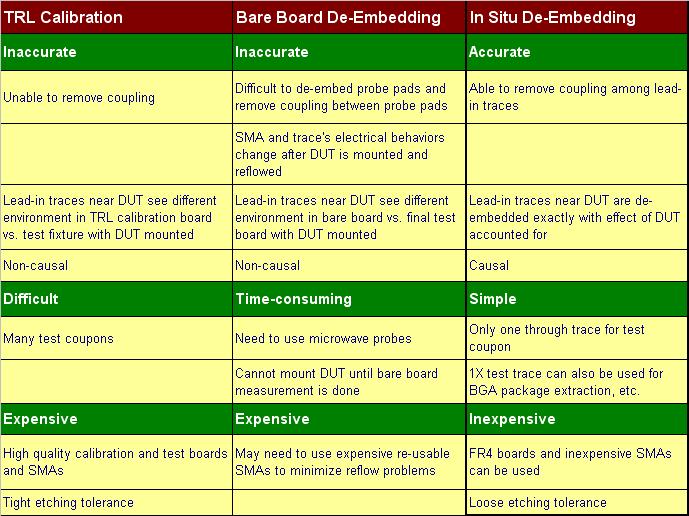

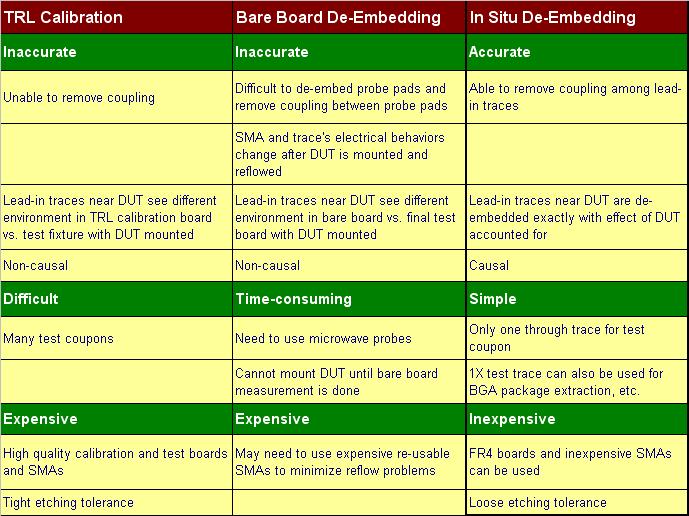

下圖整理了 ISD 軟體的 De-Emdedding 功能相較於 TRL 以及 bare board de-embedding 如何能更精確,經濟以及容易使用。

|